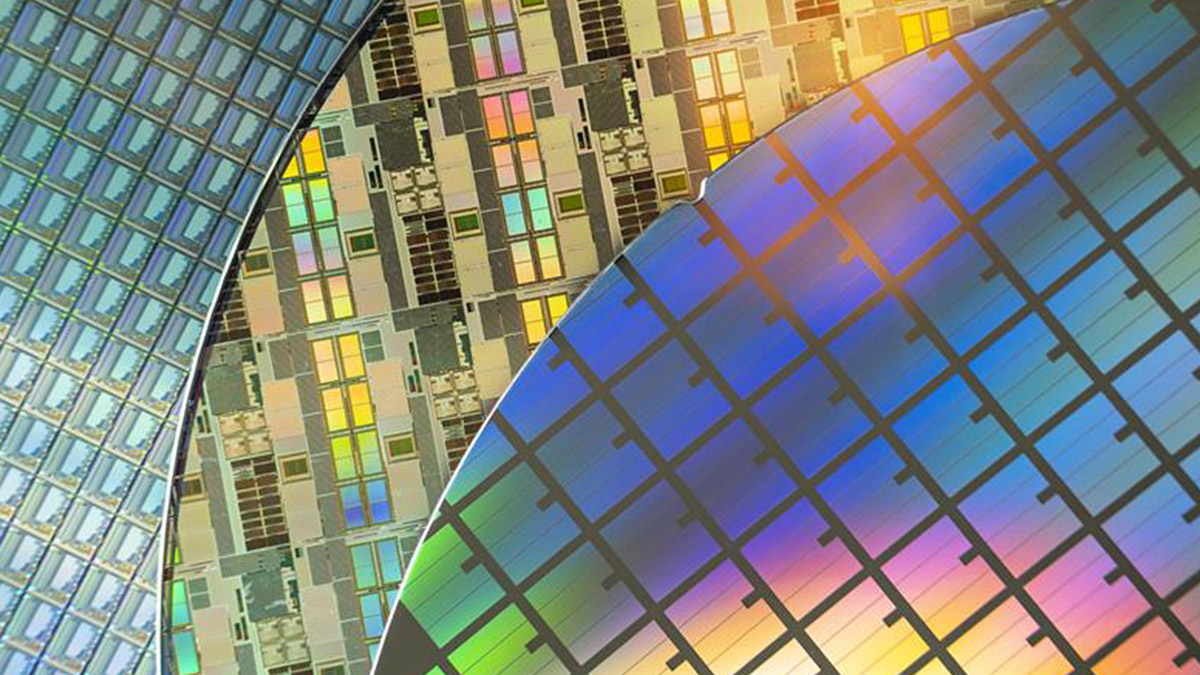

西門子數位工業軟體日前進一步深化與台積公司(台積電)的合作,共同推動半導體設計和整合領域創新,協助客戶應對下一代技術挑戰。西門子包含 nmDRC、nmLVS、YieldEnhancer™ 及 PERC™ 在内的 Calibre® nmPlatform 軟體套件,以及 Analog FastSPICE(AFS)和 Solido™ 解決方案,目前已獲得台積電 N2P 和 A16 製程認證。

此外,Calibre® 3DSTACK 解決方案已獲得台積電 3DFabric® 技術及 3Dblox 標準的認證,助力推動矽堆疊及封裝設計發展。

西門子和台積電在現有的 N3P 設計解決方案的基礎上,進一步推進針對台積電 N3C 技術的工具認證。雙方同時就台積電最新的 A14 技術的設計支援展開合作,為下一代設計奠定基礎。

西門子與台積電的合作有助於推進系統和半導體設計在人工智慧、汽車、超大規模運算、行動裝置等關鍵領域的發展,雙方近期取得的技術成果包括:

- Calibre® nmDRC 軟體、Calibre® nmLVS 軟體、Calibre® PERC™ 軟體以及採用 SmartFill 技術的 Calibre® YieldEnhancer™ 軟體,目前已獲得台積電先進 N2P 和 A16 製程認證,為雙方共同客戶提供最先進的簽核(sign-off)技術。Calibre® xACT™ 軟體已獲得台積電最新的 N2P 製程認證。

- 隨著 3Dblox 技術逐步成為 IEEE 標準,西門子和台積電合作驗證 Calibre® 3DSTACK 解決方案對 3Dblox 及台積電 3DFabric® 技術的支援,此項認證進一步延續雙方在台積電 3DFabric 矽堆疊與先進封裝技術熱分析領域的合作。西門子的 Innovator3D IC™解決方案現可在不同抽象層中支援 3Dblox 語言格式。

- 西門子 Analog FastSPICE(AFS)軟體獲得台積電 N2P 和 A16 製程認證,為下一代類比、混合訊號、射頻及記憶體設計提供強大解決方案。此外,AFS 工具作為台積電 N2 製程客製化設計參考流程(CDRF)的一部分,也支援台積電的可靠性感知模擬技術,可解決 IC 老化和即時自熱效應等可靠性問題。採用台積電 N2P 技術的 CDRF 亦與西門子的 Solido™ Design Environment 軟體整合,可執行進階變異感知驗證。

- 西門子透過 Calibre 3DSTACK 和 AFS 技術,並結合西門子的專業知識和台積電的先進製程技術,為台積電的緊湊型通用光子引擎(COUPE™)平台開發設計解決方案。

- 此外,西門子正針對 Aprisa™ 軟體和 mPower™ 軟體進行台積電 N2P 製程的認證,旨在為類比和數位設計提供實體實作和電遷移/IR 壓降分析。

- 西門子 EDA 與台積電已成功認證七種雲端 sign-off 生產流程,包括 Solido SPICE、Analog FastSPICE、採用 SmartFill 技術的 Calibre nmDRC 和 Calibre YieldEnhancer、Calibre nmLVS、Calibre PERC、Calibre xACT,以及 mPower 電源完整性分析流程工具。上述產品現在均可在 AWS 雲端上安全運作,並確保卓越的準確性。

西門子數位工業軟體西門子 EDA 執行長 Mike Ellow 表示:「在西門子 EDA 持續開拓新解決方案並推動半導體產業發展的過程中,與台積公司的聯盟是非常重要的一部分,這不僅豐富了我們的產品組合,也賦能雙方客戶從容應對未來的挑戰。」

台積公司先進技術業務開發處資深處長袁立本表示:「透過加強與西門子的合作,台積公司結合西門子經驗證的卓越設計解決方案與台積電頂尖技術的效能和能耗優勢,助力客戶創新。我們與包括西門子在内的開放創新平台(OIP)生態系合作夥伴持續合作,攜手推動半導體技術突破界限,開創未來。」