最近三星似乎積極度很高,除了半導體先進製程方面力求突破之外,據傳也將加碼投資 GPU 領域的布局,想正面與 NVIDIA 競爭意味濃厚,但記憶體方面的研發本就是持續進行的計畫,除了研究 4F Square DRAM單元陣列結構可望低目前 6F Square DEAM 的晶片表面積達 30% 之外,另一項就是 3D DRAM 技術。

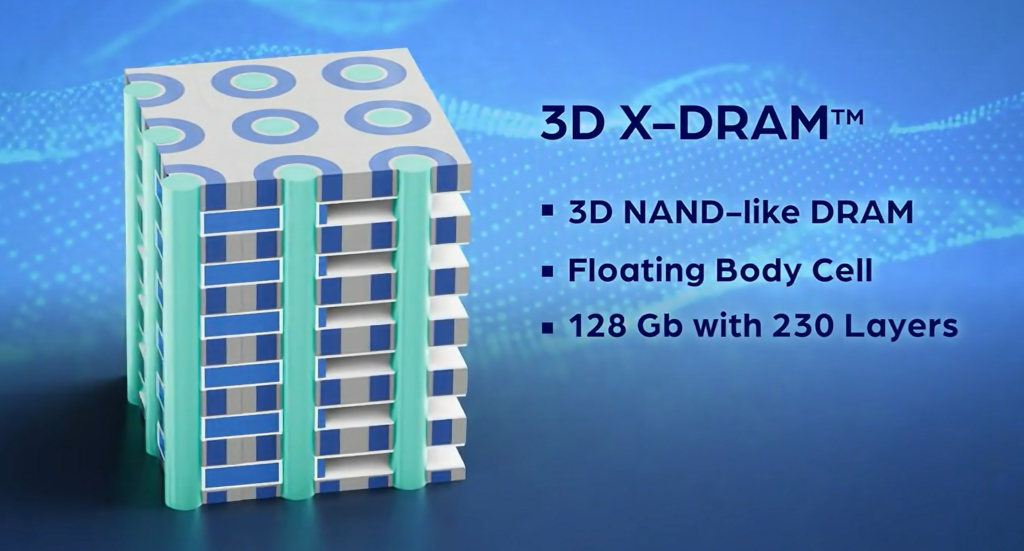

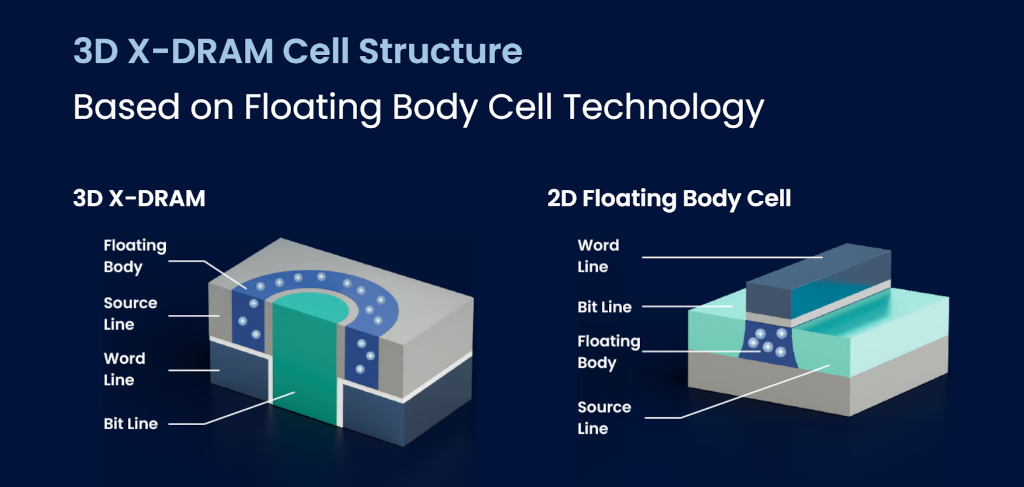

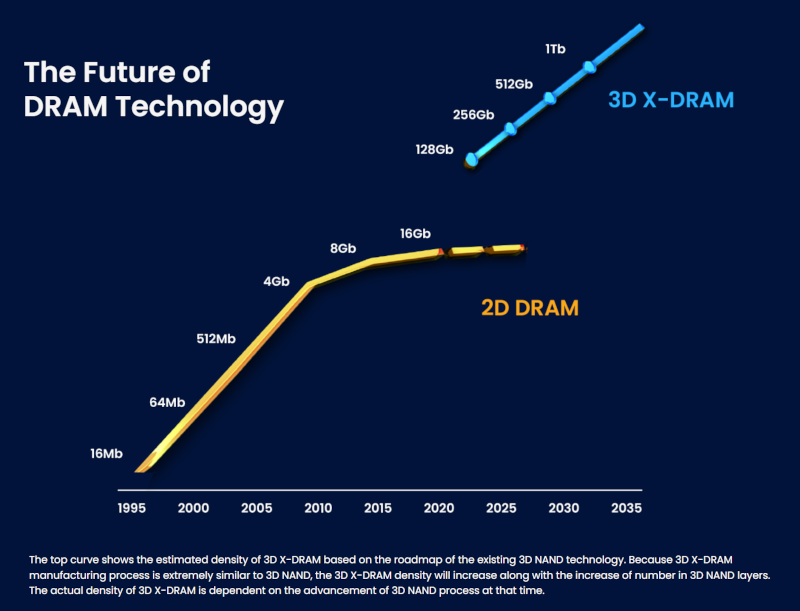

早先美國 NEO 半導體就有提出改良記憶體架構的研發方向,在 X-NAND 之後也邁入 3D DRAM 堆疊技術的圓型設計 3D X-DRAM,除了將取代 2D DRAM 市場外,也能一舉解決 DRAM 面對的容量瓶頸限制,未來記憶體也不再是 16GB,230 層堆疊就能達到 128GB、上看 512GB 甚至 1TB 也不再是遙不可及的夢想了。

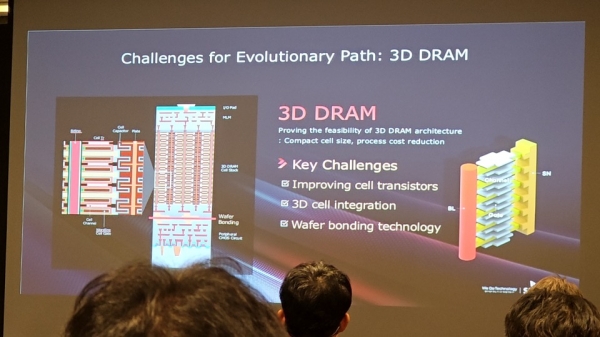

外媒TheElec 也揭露了關於 3D DRAM 的概念,就是透過 DRAM 的單元垂直堆疊,來達到提高密度的目的,也就是採用 Hybrid Bonding 混合鍵合技術,將晶片垂直堆疊通過 TSV 矽穿孔或微型銅線連接、I/O 直接連接,分成 wafer to wafer 晶元到晶元、wafer to die 晶元到晶片與 die to die 晶片到晶片等不同堆疊方式,透過垂直堆疊技術在不同晶圓上製造單元與周邊元件,就可以像 NAND 那樣做單元垂直堆疊,減少表面積擴大,提高單元密度。

目前除了三星還有 SK Hynix 也將採用,至於美光則是在研究中,不排除有加入的可能,三星木也計畫將於 2025 年推出 3D DRAM (初版)、2030 年推出堆疊式DRAM (所有單元堆疊),這也將有助於接下來在 AI 市場中的更多廣泛運用。